|

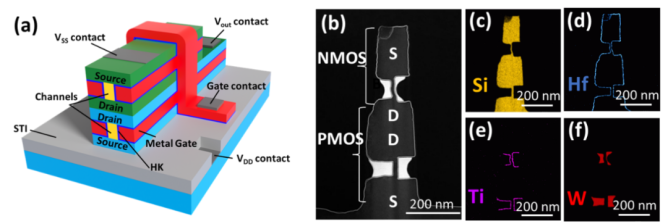

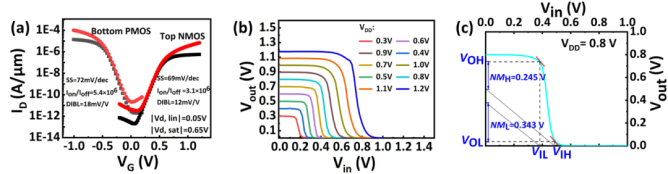

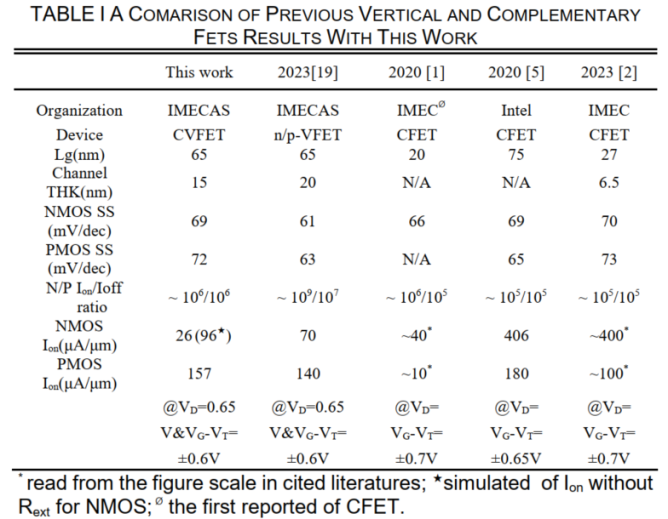

根据国际器件和系统路线图(IRDS2023),在集成电路逻辑技术领域,互补场效晶体管(CFET)是继FinFET和水平GAA之后的下一代晶体管架构。CFET技术通过将NMOS与PMOS器件垂直堆叠,改变传统平面工艺或FinFET/GAA的水平布局模式,在更小的空间内实现更高的集成密度和更佳的性能。 近日,微电子所基于自主研发的垂直沟道技术,提出和研制出一种单片集成的互补垂直沟道晶体管结构(CVFET)。该结构制造工艺采用与CMOS制造工艺兼容的双侧面技术,通过两步外延工艺分别控制纳米片沟道厚度和栅极长度,实现了n型和p型纳米片晶体管的上下堆叠和自对准一体集成。其电学特性如下:上下层(NMOS/PMOS)器件的亚阈值摆幅(SS)分别为69 mV/dec和72 mV/dec,漏致势垒降低(DIBL)分别为12 mV/V和18 mV/V,电流开关比(Ion/Ioff)分别为3.1×106和5.4×106。其CMOS反相器可实现正常的信号相位反转功能,在1.2 V的电源电压(VDD)下,反相器增益为13 V/V;在0.8 V的工作电压下,高电平噪声容限(NMH)和低电平噪声容限(NML)分别为0.343 V和0.245 V。 该研究成果以“Complementary Vertical FETs (CVFETs) Enabled by a Novel Dual-Side Process”(DOI. 10.1109/LED.2025.3587989)为题,于2025年7月正式发表在IEEE Electron Device Letters期刊上。该项研究得到了国家自然科学基金、中国科学院战略性先导专项(A类)等项目的支持。

图1:(a)单片集成CVFET器件结构图;(b) 单片集成CVFET器件的TEM截面图和(c-f)EDX元素分布图

图2:(a)单片集成CVFET器件中NMOS和PMOS器件的Id-Vg转移特性曲线;(b)CVFET反相器电压传输特性;(c)在VDD=0.8 V下,反相器的噪声容限值

|

科技视窗,专业信息资讯

中科院微电子所研发成功互补单晶硅垂直沟道晶体管(CVFET)

来源: 发布时间:2026-01-12

摘要:

下一篇:没有了

频道精选

- 中科院微电子所研发成功互补单晶硅垂直沟道2026-01-12

- 宁波空压机服务商选择指南:风源机电专业解2026-01-12

- 星空PLM需求管理方案:消费品企业决胜市场2026-01-12

- 雕刻直流电机:驱动高效雕刻的“动力心脏”2026-01-12

- IPX8级防水TYPE-C母座技术,超讯电子助力设2026-01-12

- 佛山皓迪橡胶制品如何守护我们生活的每一个2026-01-12

- 二十年淬炼,让散热更靠谱:润疆无刷风扇的2026-01-12

- 骐骥驰骋 豪沃纵横丨2026首战开门红!30台2026-01-12

- 腾悦科技共享轮椅稳居行业 全国超千家机构2026-01-12

- 金属雕塑:城市与自然的艺术对话――杭州欣2026-01-09

赛道无界,热爱不止!“喜德盛杯”2024环岛...

赛道无界,热爱不止!“喜德盛杯”2024环岛...浏览次数:0次

中科院微电子所研发成功互补单晶硅垂直沟道

浏览:0次

宁波空压机服务商选择指南:风源机电专业解浏览:0次

星空PLM需求管理方案:消费品企业决胜市场浏览:0次

雕刻直流电机:驱动高效雕刻的“动力心脏”浏览:0次

IPX8级防水TYPE-C母座技术,超讯电子助力设浏览:0次

佛山皓迪橡胶制品如何守护我们生活的每一个浏览:0次

二十年淬炼,让散热更靠谱:润疆无刷风扇的浏览:0次

骐骥驰骋 豪沃纵横丨2026首战开门红!30台浏览:0次

腾悦科技共享轮椅稳居行业 全国超千家机构浏览:0次